# GENERIC PHY FRAMEWORK: AN OVERVIEW

Kishon Vijay Abraham I

#### **About Me**

- Working in Texas Instruments since 2007

- Contributing to linux kernel for the past four years

- Develop and Maintain PHY Subsystem (drivers/phy)

- Develop and Maintain PCIe glue for DRA7xx

- USB DWC3 driver support in u-boot

- Presented a paper on "USB Debugging and Profiling Techniques" in ELCE 2012

# **Agenda**

- Introduction

- Functionalities

- PHY Standards

- PHY Integration

- PIPE3 PHY

- Generic PHY Framework

- Sample PHY/Controller Driver

- DT Representation

- Non-dt Support

- Future Enhancements

#### Introduction

- PHY is an abbreviation for the physical layer

- Responsible for transmitting data over a physical medium

- PHY connects the device controller with the physical medium

- USB

- SATA

- PCIE

- ETHERNET

### **Functionalities**

- Serialization/De-serialization

- Encoding/Decoding

- Synchronization

- Error Correction

- Collision Detection

- Data transmission rate

### **PHY Standards**

- ULPI

- UTMI+

- PIPE3

- D-PHY

- M-PHY

- IEEE 802.3

#### PHY INTEGRATION

- PHY integrated within the controller

- Shares the same address space with the controller

- No separate PHY driver is required

- PHY integrated within the SoC

- Connected to the controller using UTMI, PIPE3 interface specification

- Should have a separate PHY driver

- PHY external to the SoC

- Connected to the controller using ULPI etc..

- Should have a separate PHY driver

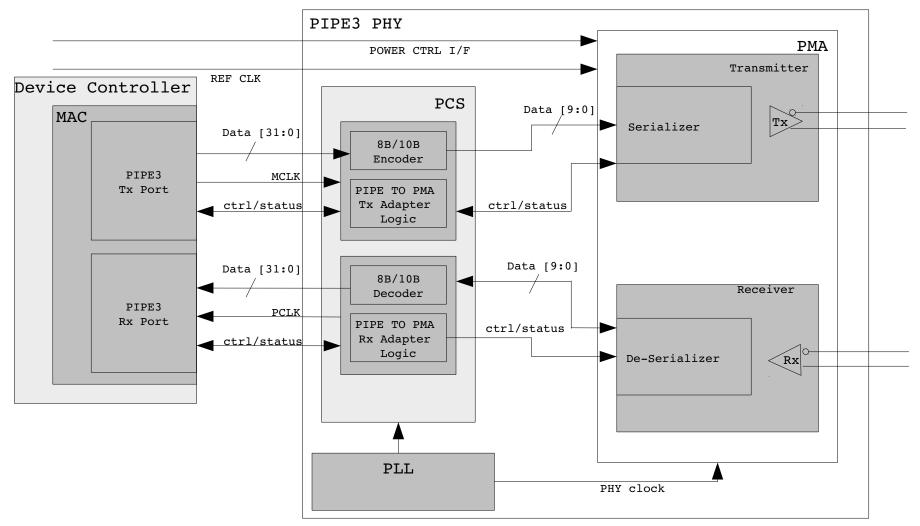

### **PIPE3 PHY**

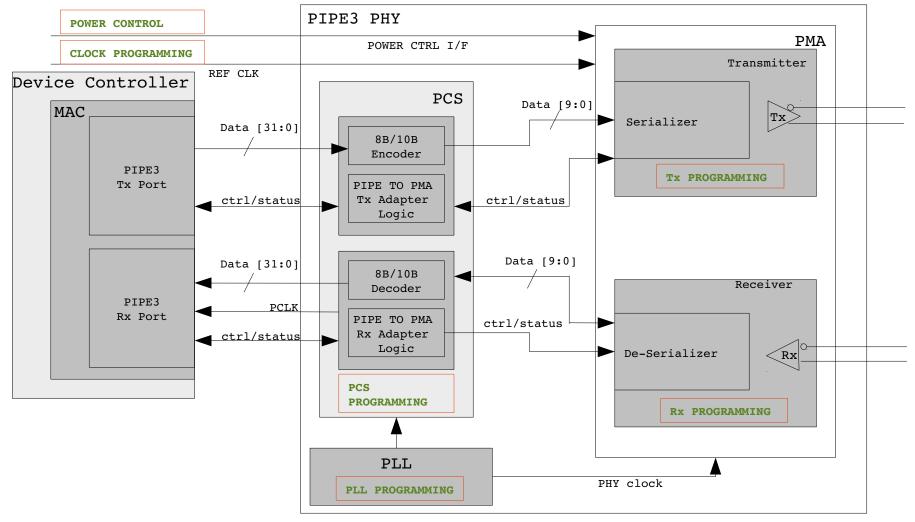

### **PIPE3 PHY PROGRAMMING**

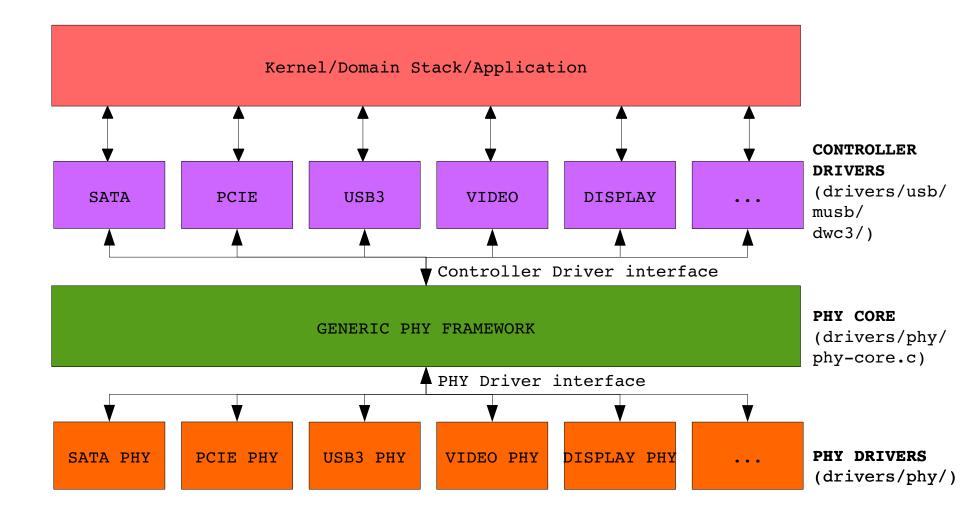

#### **Generic PHY Framework**

#### **Generic PHY Framework**

- Derived from USB PHY Framework

- Binds controller driver with PHY driver

- PHYs integrated outside the controller

- Supports dt and non-dt boot

- Op's the controller driver can use to control the PHY

- phy\_init

- phy\_power\_on

- phy\_power\_off

- phy exit

- phy\_pm\_runtime\_\*

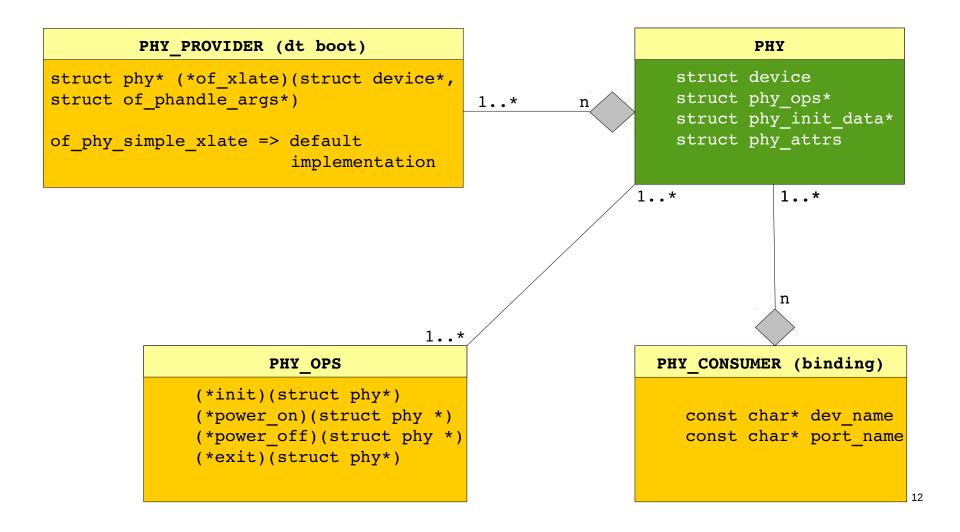

# **Phy-core Framework**

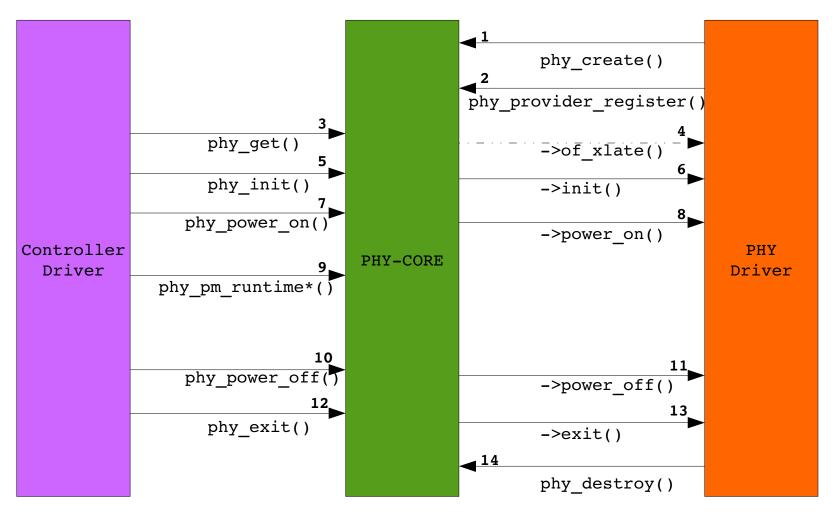

### **Sequence Diagram**

### Sample PHY driver

```

drivers/phy/phy-sample.c

static int sample phy init(struct phy *phy) {

/* Initialize Sample PHY */

}

static int sample phy power on(struct phy *phy) {

/* Enable clocks and

power on Sample PHY */

}

static int sample phy power off(struct phy *phy) {

/* Disable clocks and

power off Sample PHY */

}

static int sample phy exit(struct phy *phy) {

/* Sample PHY cleanup */

}

```

### **Sample PHY driver**

```

struct phy ops sample phy ops {

.init = sample phy init,

.power on = sample phy power on,

.power off = sample phy power off,

.exit = sample phy exit,

};

/* Sample PHY specific implementation of of xlate.

* sets the PHY to the mode obtained from of phandle args.

* If the PHY provider implements multiple PHYs, then this of xlate should

* find the correct PHY from the np present in of phandle args and return it

*/

static struct phy *sample phy xlate(struct device *dev,

struct of phandle args *args) {

sample->mode = args->args[0];

return sample->phy;

}

```

### **Sample PHY driver**

```

static int sample phy probe(struct platform device *pdev) {

phy = devm phy create(dev, dev->of node, &sample phy ops, pdata->init data);

if (dev->of node) {

/* use default implementation of of xlate if the device tree node

* represents a single PHY and if the PHY driver does not want to

* receive any arguments that's added along with the phandle

*/

// phy provider = devm of phy provider register(phy->dev,

of phy simple xlate);

phy provider = devm of phy provider register(phy->dev,

sample phy xlate);

```

### **Sample Controller driver**

```

drivers/<controller>/controller-sample.c

static int sample controller probe(struct platform device *pdev) {

phy = devm phy get(dev, "sample-phy");

}

int sample controller init() {

/* controller initialization goes here */

phy init(phy);

}

int sample controller start transfer() {

phy power on(phy);

/* program the controller to start transfer */

}

int sample controller complete transfer() {

/* free buffer etc */

phy power off(phy);

```

#### **DT REPRESENTATION**

- Single PHY

- Multi PHY

- Multiple instances of the same PHY

- Single PHY IP encompasses multiple PHYs

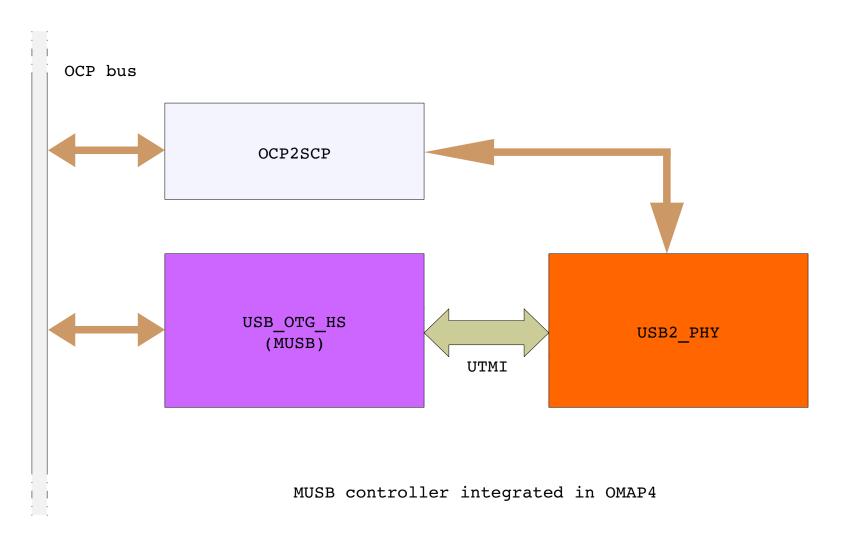

# **Single PHY**

# **Single PHY (dt representation)**

```

ocp2scp@xxxxx {

compatible = "ti,omap-ocp2scp";

usb2phy@0 {

compatible = "ti,omap-usb2";

#phy-cells = <0>;

usb otg hs@xxxxx {

compatible = "ti,omap4-musb";

phys = <&usb2phy>;

phy-names = "usb2-phy";

```

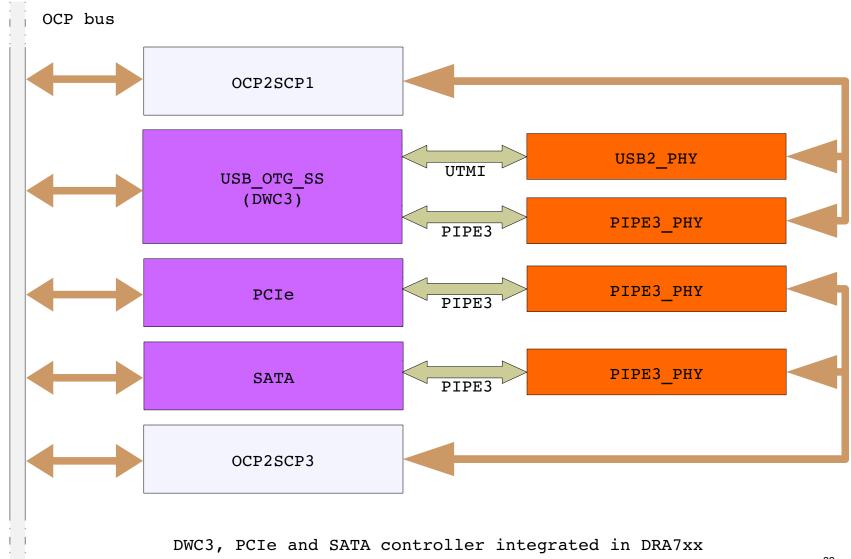

# Multi PHY (Multiple instances of same IP)

# Multi PHY (dt representation)

```

ocp2scp3@xxxxx {

pcie@0 {

compatible = "ti,omap-ocp2scp";

compatible = "ti,dra7-pcie";

pciephy: pipe3phy@0 {

compatible = "ti,phy-pipe3";

phys = <&pciephy PCIEPHY>;

phy-names = "pcie-phy";

#phy-cells = <1>;

}

sataphy: pipe3phy@1 {

compatible = "ti,phy-pipe3";

sata@0 {

compatible = "snps,dwc-ahci";

#phy-cells = <1>;

phys = <&sataphy SATAPHY>;

phy-names = "sata-phy";

ocp2scp1@xxxxx {

compatible = "ti,omap-ocp2scp";

usb3phy: pipe3phy@0 {

compatible = "ti,phy-pipe3";

usb otg ss@xxxxx {

compatible = "snps,dwc3";

\#phy-cells = <1>;

phys = <&usb2phy>, <&usb3phy USBPHY>;

usb2phy@0 {

phy-names = "usb2-phy", "usb3-phy";

compatible = "usb2-phy";

#phy-cells = <0>;

}

23

```

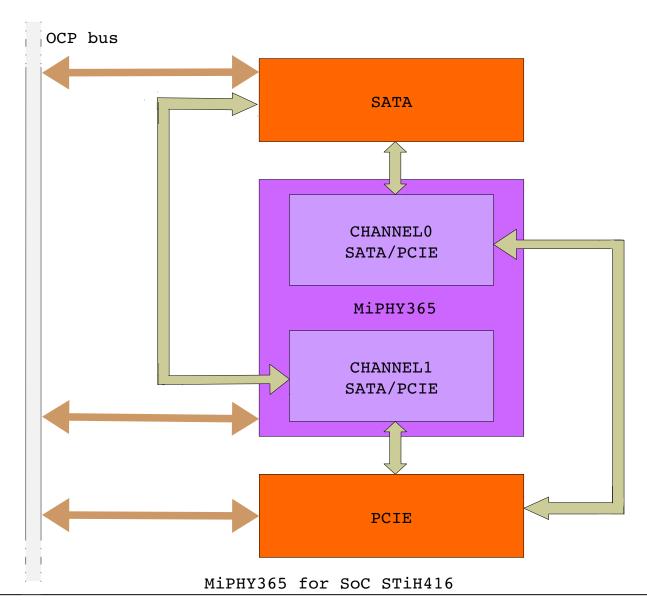

Multi PHY (Single IP encompass multiple

phys)

## Multi PHY (dt representation)

```

sata0: sata@fe380000 {

miphy: miphy365x@fe382000 {

compatible = "st,miphy365x-phy";

phys = <&phy port0 MIPHY TYPE SATA>;

phy-names = "sata-phy";

phy port0: port@fe382000 {

};

#phy-cells = <1>;

}

phy port1: port@fe38a000 {

#phy-cells = <1>;

};

};

OLD METHOD

sata0: sata@fe380000 {

miphy: miphy365x@fe382000 {

compatible = "st,miphy365x-phy";

phys = <&miphy 0 MIPHY TYPE SATA>;

phy-names = "sata-phy";

#phy-cells = <2>;

};

};

```

### **Non-dt Support**

- PHYs should be aware of their consumers

- Consumer data is added as platform data to the platform device

- PHY driver should pass it to phy-core during phy\_create()

```

struct phy_consumer consumers[] = {

PHY_CONSUMER("musb-hdrc.0", "usb"),

};

struct phy_init_data init_data = {

.consumers = consumers,

.num_consumers = ARRAY_SIZE(consumers),

};

```

#### **Future Enhancements**

- Adapt existing PHY drivers to Generic PHY Framework

- Support for ULPI PHY driver

- Support for Ethernet PHYs

# **Upstreamed PHY drivers (3.17)**

| PHY                  | Domain               | Vendor             |

|----------------------|----------------------|--------------------|

| Kona PHY             | USB2                 | Broadcom           |

| Berlin PHY           | SATA                 | Marvell            |

| Exynos PHY           | USB2, SATA, DISPLAY, | Samsung            |

| HIX5HD2 SATA PHY     | SATA                 | Hisilicon          |

| МІРНУ365             | SATA, PCIE           | STMicroelectronics |

| MVEBU PHY            | SATA                 | Marvell            |

| OMAP USB2 PHY        | USB2                 | Texas Instruments  |

| APQ8064 PHY          | SATA                 | Qualcom            |

| IPQ806X PHY          | SATA                 | Qualcom            |

| S5PV210 PHY          | USB2                 | Samsung            |

| SPEAR1310/1340 MIPHY | SATA, PCIE           | STMicroelectronics |

| SUN4I USB PHY        | USB                  | Allwinner          |

| TI PIPE3             | SATA, PCIE, USB3     | Texas Instruments  |

| X-GENE PHY           | SATA                 | Applied Micro      |

## **Acknowledgements**

- Felipe Balbi

- Greg KH

- Everyone who has contributed to PHY (Authors, Reviewers, Testers etc..)

### References

- wikipedia.org/wiki/Physical\_layer

- mipi.org/specifications/physical-layer

- PIPE specification

- drivers/phy/

- Documentation/phy.txt

#### **THANK YOU**

### **For Queries and Feedback**

kishon@ti.com, kishonvijayabraham@gmail.com