# Linux Kernel Power Management (PM) Framework for ARM 64-bit Processors

L.Pieralisi

21/8/2014 - LinuxCon North America 2014

#### Outline

ARM 32-bit Linux kernel power management support for huge legacy of ARM processors

- from v4 Uniprocessor kernels to ARM v7 SMP multicluster systems

- Lack of established firmware interfaces is preventing merge of power management software in the mainline kernel

- Lots of tricky platform specific code, maintained as out of tree BSP branches

- Power management HW dependent SW layers incompatible with most of kernel SW interfaces

- ARM64 kernel port represents an opportunity to start afresh and learn lessons from the past

#### Legacy ARM 32-bit Linux Kernel Power Management

- Standards ? No, thanks

- ARM vendors power controllers

- Differentiating through design quirks

- Standard power down procedures started appearing on ARM v7 TRMs

- What works on ARM v7, might not on v6, and viceversa

- ARM v7 power down procedure is standard, except for when it is not

- …and then came SMP systems….

- Kernel developers left to their own devices

- Reverse engineering (lack of publicly available specs)

- Power management interfaces designed for UP systems did not work on SMP

- Secure/non-secure split overriden in most upstream design

- Kernel subsystems (eg CPUidle) redesigned to support HW bugs (eg couple idle states)

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

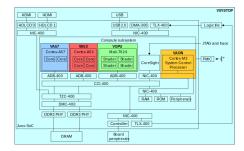

#### **ARM Chips Power Management Configurations**

- Multiple power islands

- Devices and CPUs power domains

- Core gating and Cluster gating

- RAM retention states

- Caches management

- Coherency management

- Locking

- Graphics power domain

- Integration with CPU states

- System sleep states

- Always-on power domain

(日)

## ARM Power Management HW/SW stack (1/2)

Cross-divisional collaborative effort between ARM SW/HW engineers

- HW prototyping effort (TC2/Juno)

- Power controller specifications

- SW stack (Linux kernel/Trusted Firmware/power controller firmware)

- Tackle ARM vendors power control fragmentation

- Power management HW still a prominent feature of vendors design

(日)

- Design quirks are the rule, not the exception

- Ongoing effort at ARM to standardize main HW control feaures

- HW SMP coherency management

- Cache clean and invalidate (SW/HW)

- Wake-up capabilities and GIC design

#### ARM Power Management HW/SW stack (2/2)

- Development and deployment of PSCI (Power State Coordination Interface) firmware interface

- Device tree and ACPI bindings standardization

- Provide OS with standard interfaces

- Configuration data for power management subsystems (CPU/device idle states)

- Run-time services (CPU/devices power management)

#### **Our Goal**

$\label{eq:provide a HW/SW environment to foster power management standardization$

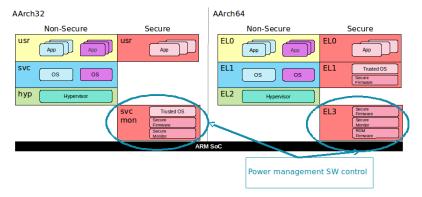

#### **ARM Power Management: Secure Operations**

- Power management SW has to deal with secure operations

- Coherency management, power control commands

- Need for a standard API to communicate to secure world

・ロト ・ 『 ト ・ ヨ ト ・ ヨ ト

3

#### **ARM Power Management: Secure Operations**

"... I guess what this ultimately comes down to is that we \_did\_ accept the work-arounds into the kernel source for secure parts - had we not done that and set a clear message like ARM64 does that work-arounds must be done prior to calling the kernel (irrespective of how that happens, iow, whether boot or resume) then we wouldn't have this problem right now. Such a statement would have raised lots of objections though, but with hindsight, it would have been the right thing to do to overrule those objections and just mandate it. It would've been a pain for some people, but we would not be in this situation now where there is no proper solution which works for everyone."

#### RMK

http://lists.infradead.org/pipermail/linux-arm-kernel/ 2014-July/268718.html

#### **ARM Power Management: Early Devices**

```

int __init ve_spc_init(void __iomem *baseaddr,

2

void ve_spc_set_resume_addr(u32 cluster, u32 cpu,

u32 a15_clusid, int irq)

1

з

^{2}_{3}

u32 addr)

4

int ret;

5

info = kzalloc(sizeof(*info), GFP KERNEL);

^{4}

void iomem *baseaddr:

6

\mathbf{5}

if (!info) {

\overline{7}

return -ENOMEM:

6

if (cluster >= MAX CLUSTERS)

8

7

return:

9

8

10

9

info->baseaddr = baseaddr:

if (cluster is a15(cluster))

11

10

info->a15 clusid = a15 clusid:

baseaddr = info->baseaddr +

12

11

A15 BX ADDR0 + (cpu << 2);

13

ſ...1

12

else

13

14

baseaddr = info->baseaddr +

15

sync cache w(info):

14

A7 BX ADDR0 + (cpu << 2):

16

svnc cache w(&info):

15

17

16

writel relaxed(addr. baseaddr):

17

18

return 0:

19

```

- Need to probe device drivers early (before early\_initcalls)

- Power controllers drivers

- CPU memory mapped peripherals (no access through coprocessor need DT probing)

イロト 不得 トイヨト イヨト 三日

- Resulting code incompatible with kernel driver model

- Code exiled to arch/arm, because it does not belong anywhere else

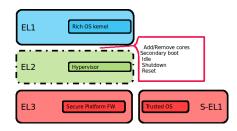

#### **Power State Coordination Interface**

- Defines a standard interface for making power management requests across exception levels/operating systems

- Support virtualisation and a communication channel between normal and secure world

- Allow secure firmware to arbitrate power management requests from secure and non-secure software

- Default method for power control in Linux ARM64 kernel

- CPU on/off (hotplug, cold-boot)

- CPU suspend (suspend to RAM, CPUidle)

- Spec available at

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc. den0022b/index.html

#### **ARM64 Linux Power Management Requirements**

- Reliance on PSCI as firmware interface

- Trusted firmware PSCI implementation publicly available for FVP models and Juno

https://github.com/ARM-software/arm-trusted-firmware

- Device tree and ACPI bindings to standardize control data and improve code generality

- Take part in ACPI standardization effort http://www.acpi.info

- Actively push for Device Tree bindings for power management SW components

- Push back on design quirks and related SW hacks

- More collaboration between ARM and ARM partners on HW/SW interfaces

- HW standardization effort must be deployed in ARM vendors designs

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

・

SW interfaces adopted by ARM partners Linux kernel developers

#### Linux Kernel Power Management Subsystems

CPUidle: framework managing idle threads

- CPUs enter idle states when idling, with power depth levels that depend on power management HW

- CPU hotplug: removing a CPU from a running system

- Not designed for power management, abused as such

- Runtime PM

- Devices power management

- Suspend to RAM: system wide (CPU and devices) sleep states

- Triggered from userspace, also used as autosuspend when system is idle (eg on Android)

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

Suspend to disk (aka Hibernation): same as Suspend-to-RAM, system image saved to disk instead of volatile memory

#### Linux Kernel PM example: CPUidle core

#### CPU is running idle

- Next event (in time) determines how long the CPU can sleep

- CPU woken up by IRQs, behaves as WFI regardless of the idle state power depth

- Idle state entered through CPUidle driver enter() function

- Prepare the CPU for power down

- Execute the power down command

| 1      | CPU idle state data                        |  |  |  |

|--------|--------------------------------------------|--|--|--|

| 2      |                                            |  |  |  |

| 3      | struct cpuidle_state {                     |  |  |  |

| 4      | <pre>char name[CPUIDLE_NAME_LEN];</pre>    |  |  |  |

| 5      | <pre>char desc[CPUIDLE_DESC_LEN];</pre>    |  |  |  |

| 6<br>7 | unsigned int flags;                        |  |  |  |

| 7      | unsigned int exit_latency; /* in US */     |  |  |  |

| 8      | int power_usage; /* in mW */               |  |  |  |

| 9      | unsigned int target_residency; /* in US */ |  |  |  |

| 10     | bool disabled; /* disabled on all CPUs */  |  |  |  |

| 11     | /* Idle state enter function */            |  |  |  |

| 12     | {int (*enter)(struct cpuidle_device *dev,  |  |  |  |

| 13     | struct cpuidle_driver *drv,                |  |  |  |

| 14     | int index);                                |  |  |  |

| 15     |                                            |  |  |  |

| 16     | };                                         |  |  |  |

|        |                                            |  |  |  |

#### ARM 32-bit CPUidle consolidation issues

- Current ARM CPUidle drivers in the kernel cannot be easily cleaned-up/consolidated

- ARM 32-bit SMP CPUidle code was merged separately through different trees, with no consolidation effort

- cpu\_suspend() kernel interface was defined, but there are still open issues that prevent consolidation

- Lack of standard power down procedures

- Lack of standard idle state entry interface

- Multi-Cluster Power Management (MCPM) introduction helped define a common entry point for idle

- It requires the kernel to run in secure world unless security is overriden in firmware

It relies on early devices initialization in the kernel

#### ARM 32-bit CPUidle consolidation issues

- Current ARM CPUidle drivers in the kernel cannot be easily cleaned-up/consolidated

- ARM 32-bit SMP CPUidle code was merged separately through different trees, with no consolidation effort

- cpu\_suspend() kernel interface was defined, but there are still open issues that prevent consolidation

- Lack of standard power down procedures

- Lack of standard idle state entry interface

- Multi-Cluster Power Management (MCPM) introduction helped define a common entry point for idle

- It requires the kernel to run in secure world unless security is overriden in firmware

It relies on early devices initialization in the kernel

# ARM 32-bit v7 shutdown procedure (1/3)

```

ENTRY(tegra_disable_clean_inv_dcache)

1

2

stmfd

sp!, {r0, r4-r5, r7, r9-r11, lr}

з

dmb

@ ensure ordering

4

\mathbf{5}

/* Disable the D-cache */

6

mrc

p15, 0, r2, c1, c0, 0

7

bic

r2, r2, #CR C

8

p15, 0, r2, c1, c0, 0

mcr

9

ish

10

11

/* Flush the D-cache */

12

r0, #TEGRA FLUSH CACHE ALL

CMD

13

blne

v7 flush dcache louis

14

blea

v7 flush dcache all

15

16

/* Turn off coherency */

17

exit smp r4. r5

18

19

ldmfd sp!, {r0, r4-r5, r7, r9-r11, pc}

20

ENDPROC(tegra_disable_clean_inv_dcache)

```

https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/tree/ arch/arm/mach-tegra/sleep.S?id=refs/tags/v3.16

イロト イボト イヨト イヨト 三日

# ARM 32-bit v7 shutdown procedure (2/3)

| 2 stafd sp!, fr4-r12, lr}<br>3 cmp r0, #0x0<br>4 beq do_WFI 0 No lowpower state, jump to WFI<br>5 []<br>6 skip.secure_l1_clean:<br>7 bl v7_flush_dcache_all<br>8 mrc p15, 0, r0, c1, c0, 0<br>10 bic r0, r0, #(1 << 2) 0<br>11 mcr p15, 0, r0, c1, c0, 0<br>12 isb<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1       | ENTRY(omap4_finish_suspend) |                       |                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|-----------------------|----------------------------------|--|

| 4       beq       do_WFI       @ No lowpower state, jump to WFI         5       []       skip_secure_11_clean:         7       bl       v7_flush_dcache_all         8           9       mrc       p15, 0, r0, c1, c0, 0         10       bic       r0, r0, f1(<<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2       | stmfd                       | sp!, {r4-r12, lr}     |                                  |  |

| <pre>5 [] 6 skip_secure_ll_clean: 7 bl v7_flush_dcache_all 8 9 mrc p15, 0, r0, c1, c0, 0 10 bic r0, r0, #(1 &lt;&lt; 2)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3       | cmp                         | r0, #0x0              |                                  |  |

| 6       skip_secure_ll_clean:         7       bl       v7_flush_dcache_all         9       mrc       p15,0,r0,c1,c0,0         10       bic       r0,r0,#(1<<2.2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | beq                         | do_WFI                | @ No lowpower state, jump to WFI |  |

| 7       b1       v7_flush_dcache_all         9       mrc       p15, 0, r0, c1, c0, 0         10       bic       r0, r0, #(1 << 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | []                          |                       |                                  |  |

| 8         Image of the state of the st |         | skip_secure_11_clean:       |                       |                                  |  |

| 9       mcc       p15, 0, r0, c1, c0, 0         10       bic       r0, r0, #(1 << 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | bl                          | v7_flush_dcache_all   |                                  |  |

| 10     bic     r0, r0, #(1 << 2)     @Disable the C bit       11     mcr     p15, 0, r0, c1, c0, 0     0       12     isb       13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                             |                       |                                  |  |

| 11       mcr       p15, 0, r0, c1, c0, 0         12       isb         13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                             |                       |                                  |  |

| <pre>12 isb 13 14 bl v7_flush_dcache_all 15 16 bl omap4_get_sar_ram_base 17 mov r8, r0 18 ldr r9, [r8, #OMAP_TYPE_OFFSET] 19 cmp r9, #0x1 © Check for HS device 20 bne scu_gp_set 21 mrc p15, 0, r0, c0, c0, 5 © Read MPIDR 22 ands r0, r0, #0x0f 23 ldreq r0, [r8, #SCU_OFFSET0] 24 ldrme r0, [r8, #SCU_OFFSET1] 25 mov r1, #0x00 26 stmfd r13!, {r4-r12, r14} 27 ldr r12, =OMAP4_MON_SCU_PWR_INDEX 28 D0_SNC 29 []</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                             |                       | @Disable the C bit               |  |

| 13     bl     v7_flush_dcache_all       14     bl     omap4_get_ssr_ram_base       15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                             | p15, 0, r0, c1, c0, 0 |                                  |  |

| 14     b1     v7_flush_dcache_all       15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | isb                         |                       |                                  |  |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                             |                       |                                  |  |

| 16     b1     omap4_get_sar_ram_base       17     mov     r8, r0       18     ldr     r9, [r8, #0MAP_TYPE_0FFSET]       19     mp     r9, #0x1     @ Check for HS device       20     bne     scu_gp_set       21     mcc     p15, 0, r0, c0, c0, 5     @ Read MPIDR       23     ldreq     r0, [r8, #SCU_0FFSET]]       24     ldrne     r0, [r8, #SCU_0FFSET]]       25     mov     r1, #0x00       26     stmfd     r13!, {r4-r12, r14}       27     ldr     r12, =0MAP4_MON_SCU_PWR_INDEX       28     D0_SNC       29     []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | DT                          | v/_flusn_dcache_all   |                                  |  |

| 17     mov     r8, r0       18     ldr     r9, [r8, #0MAP_TYPE_OFFSET]       19     cmp     r9, #0x1     © Check for HS device       20     bme     scu_gp_set       21     mrc     p15, 0, r0, c0, c0, 5     @ Read MPIDR       22     ands     r0, r0, #0x0f       23     ldreq     r0, [r8, #SCU_OFFSET0]       24     ldrme     r0, [r8, #SCU_OFFSET1]       25     mov     r1, #0x00       26     stmfd     r13!, {r4-r12, r14}       27     ldr     r12, =0MAP4_MON_SCU_PWR_INDEX       28     D0_SNC       29     []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | 1.1                         |                       |                                  |  |

| 18     ldr     r9, [r8, #OMAP_TYPE_OFFSET]       19     cmp     r9, #OX1     © Check for HS device       20     bne     scu_gp_set       21     mrc     pl5, 0, r0, c0, c0, 5     @ Read MPIDR       22     ands     r0, r0, #Ox07       23     ldreq     r0, [r8, #SCU_OFFSET0]       24     ldrne     r0, [r8, #SCU_OFFSET1]       25     mov     r1, #0x00       26     stmfd     r13!, {r4-r12, r14}       27     ldr     r12, =OMAP4_MON_SCU_PWR_INDEX       28     D0_SMC       29     []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                             |                       |                                  |  |

| 19     cmp     r9, #0x1     @ Check for HS device       20     bme     scu_gp_set       21     mrc     p15, 0, r0, c0, c0, 5     @ Read MPIDR       22     ands     r0, r0, #0x0f       23     ldreq     r0, [r8, #SCU_OFFSET0]       24     ldrne     r0, [r8, #SCU_OFFSET0]       25     mov     r1, #0x00       26     stmfd     r13!, {r4-r12, r14}       27     ldr     r12, =OMAP4_MON_SCU_PWR_INDEX       28     D0_SNC       29     []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                             |                       |                                  |  |

| 20         bm         scu_gp.st           21         mrc         p15,0,r0,c0,c0,5         @ Read MPIDR           22         ands         r0,r0,#0x0f            23         ldreq         r0,r0,#0x0f            24         ldreq         r0,[r8,#SCU_GFFSET0]            25         mov         r1,#0x00            26         stmfd         r13!, {r4-r12, r14}           27         ldr         r12, =0MAP4_MON_SCU_FWR_INDEX           28         D0_SMC            29         []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                             |                       | Check for US device              |  |

| 21         mrc         p15,0,r0,c0,c0,5         @ Read MPIDR           22         ands         r0,r0,#0x0f         dega         ndga           23         ldreg r0,[r8,#SCU_0FFSET0]         dega         ndga         ndga           24         ldrne r0,[r8,#SCU_0FFSET1]         dega         ndga         ndga           25         mov r1,#0x00         dega         ndga         ndga           26         stmfd r131, {r4-r12, r14}         dr         r12, =0MAP4_MON_SCU_PWR_INDEX         dega         D0_SNC           29         []         dega                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | -                           |                       | a cueck ioi up device            |  |

| 22     ands     r0, r0, #0x0f       23     ldreq     r0, [r6, #5CU_DFFSET0]       24     ldrene     r0, [r6, #5CU_DFFSET1]       25     mov     r1, #0x00       26     stmfd     r13!, {r4-r12, r14}       27     ldr     r12, =0MAP4_MON_SCU_PWR_INDEX       28     D0_SNC       29     []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                             |                       | @ Read MPTDR                     |  |

| 23     ldreq     r0, [r8, #SCU_OFFSET0]       24     ldrne     r0, [r8, #SCU_OFFSET1]       25     mov     r1, #0x00       26     stmfd     r13, {r4-r12, r14}       27     ldr     r12, =0MAP4_MON_SCU_PWR_INDEX       28     D0_SMC       29     []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                             |                       | a noda in ibn                    |  |

| 24     ldrne r0, [r8, #SCU_OFFSET1]       25     mov r1, #0x00       26     stmfd r131, {r4-r12, r14}       27     ldr r12, =OMAP4_MON_SCU_PWR_INDEX       28     D0_SMC       29     []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                             |                       |                                  |  |

| 25         mov         r1, #0X00           26         stmfd         r13!, {r4-r12, r14}           27         ldr         r12, =0MAP4_MON_SCU_PWR_INDEX           28         D0_SMC           29         []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                             |                       |                                  |  |

| 26         stmfd ri3!, {r4-r12, r14}           27         ldr r12, =OMAP4_MON_SCU_PWR_INDEX           28         D0_SNC           29         []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25      | mov                         |                       |                                  |  |

| 28 D0_SMC<br>29 []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26      | stmfd                       |                       |                                  |  |

| 29 []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27      | ldr                         |                       |                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $^{28}$ | D0_SMC                      |                       |                                  |  |

| 30 ENDPROC(omap4 finish suspend)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $^{29}$ | []                          |                       |                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30      | ENDPROC(omap4_f             | inish_suspend)        |                                  |  |

https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/tree/ arch/arm/mach-omap2/sleep44xx.S?id=refs/tags/v3.16

# ARM 32-bit v7 shutdown procedure (3/3)

```

#define v7 exit coherency flush(level) \

1

2

asm volatile( \

3

"stmfd

sp!, {fp, ip} \n\t" \

4

p15, 0, r0, c1, c0, 0

@ get SCTLR \n\t" \

"mrc

\mathbf{5}

r0, r0, #"__stringify(CR_C)" \n\t" \

"bic

6

p15, 0, r0, c1, c0, 0

@ set SCTLR \n\t" \

"mcr

7

"isb

\n\t" \

8

v7 flush dcache " stringifv(level)" \n\t" \

"h1

9

"clrey

\n\t" \

10

p15, 0, r0, c1, c0, 1

@ get ACTLR \n\t" \

"mrc

11

@ disable local coherency \n\t" \

"bic

r0, r0, #(1 << 6)

12

"mcr

p15, 0, r0, c1, c0, 1

@ set ACTLR \n\t" \

13

nt" \

"isb

14

nt" \

"dsb

15

"ldmfd

sp!, {fp, ip}" \

16

: : : "r0","r1","r2","r3","r4","r5","r6","r7", \

17

"r9", "r10", "lr", "memory" )

```

https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/tree/ arch/arm/include/asm/cacheflush.h?id=refs/tags/v3.16

#### ARM 32-bit CPUidle consolidation issues

- Current ARM CPUidle drivers in the kernel cannot be easily cleaned-up/consolidated

- ARM SMP CPUidle code merged separately through different trees, with no consolidation effort

- cpu\_suspend() kernel interface was defined, but there are still open issues that prevent consolidation

- Lack of standard power down procedures

- Lack of standard idle state entry interface

- Multi-Cluster Power Management (MCPM) introduction helped define a common entry point for idle

- It requires the kernel to run in secure world unless security is overriden in firmware

It relies on early devices initialization in the kernel

# ARM 32-bit CPUidle enter examples (1/3)

```

static int armada_370_xp_enter_idle(struct cpuidle_device *dev,

2

struct cpuidle_driver *drv,

з

int index)

4

\mathbf{5}

int ret;

6

bool deepidle = false;

7

cpu_pm_enter();

8

9

if (drv->states[index].flags & ARMADA_370_XP_FLAG_DEEP_IDLE)

10

deepidle = true;

11

12

ret = armada_370_xp_cpu_suspend(deepidle);

13

if (ret)

14

return ret;

15

16

cpu_pm_exit();

17

18

return index:

19

```

https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/tree/ drivers/cpuidle/cpuidle-armada-370-xp.c?id=refs/tags/v3.16

イロト イボト イヨト イヨト 三日

#### ARM 32-bit CPUidle enter examples (2/3)

```

static int idle finisher(unsigned long flags)

1

2

3

exvnos enter aftr():

4

cpu_do_idle();

\mathbf{5}

6

return 1:

7

8

9

static int exynos_enter_core0_aftr(struct cpuidle_device *dev,

10

struct cpuidle_driver *drv,

11

int index)

12

13

cpu_pm_enter();

14

cpu_suspend(0, idle_finisher);

15

cpu_pm_exit();

16

17

return index;

18

19

20

static int exynos_enter_lowpower(struct cpuidle_device *dev,

^{21}

struct cpuidle_driver *drv,

^{22}

int index)

^{23}

^{24}

int new_index = index;

25

26

if (num_online_cpus() > 1 || dev->cpu != 0)

27

new_index = drv->safe_state_index;

^{28}

29

if (new index == 0)

30

return arm cpuidle simple enter(dev. drv. new index);

31

else

32

return exvnos enter core0 aftr(dev. drv. new index);

33

```

https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/tree/ARM drivers/cpuidle/cpuidle-exynos.c?id=refs/tags/v3.16

#### ARM 32-bit CPUidle enter examples (3/3)

```

static int notrace bl_powerdown_finisher(unsigned long arg)

2

з

/* MCPM works with HW CPU identifiers */

4

unsigned int mpidr = read_cpuid_mpidr();

\mathbf{5}

unsigned int cluster = MPIDR_AFFINITY_LEVEL(mpidr, 1);

6

unsigned int cpu = MPIDR_AFFINITY_LEVEL(mpidr, 0);

7

8

mcpm_set_entry_vector(cpu, cluster, cpu_resume);

9

[...]

10

11

mcpm_cpu_suspend(0);

12

13

/* return value != 0 means failure */

14

return 1;

15

16

17

static int bl_enter_powerdown(struct cpuidle_device *dev,

18

struct cpuidle_driver *drv, int idx)

19

20

cpu_pm_enter();

21

^{22}

cpu suspend(0, bl powerdown finisher);

23

^{24}

mcpm_cpu_powered_up();

25

26

cpu_pm_exit();

27

^{28}

return idx:

29

```

https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/tree/ drivers/cpuidle/cpuidle-big\_little.c?id=refs/tags/v3.16

◆□▶ ◆□▶ ◆□▶ ◆□▶ ●□

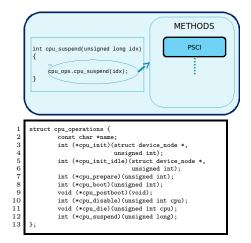

#### Linux Kernel ARM64 CPU operations

- Generic kernel interface for CPU operations

- boot

- hotplug

- idle

- CPU operations represent the interface through which the kernel carries out the required actions on CPUs

- Interface hides the actual method implementation

- Hooks initialized at boot through DT or ACPI

ARM

#### **ARM64 CPUidle enter**

```

static int arm_enter_idle_state(struct cpuidle_device *dev,

1

2

struct cpuidle_driver *drv, int idx)

з

4

int ret;

\mathbf{5}

6

if (!idx) {

7

cpu_do_idle();

8

return idx;

9

3

10

11

ret = cpu_pm_enter();

12

if (!ret) {

13

/*

14