Design and Implementation of a Security Architecture for Critical Infrastructure Industrial Control Systems in the Era of Nation State Cyber Warfare

David Safford, Bill Smith, Monty Wiseman GE Global Research Center

LSS, 2016

Imagination at work.

# Controls broad reach

### GE:

- Half of the world's installed Power Generation (PG) base is from GE

- 10,000 gas and steam turbine generating units

- Over 1,000,000 megawatts of installed capacity in 120 countries.

- https://powergen.gepower.com/products/heavy-duty-gas-turbines.html

- 40% share of the worldwide market for new PG equipment.

- <a href="http://www.statista.com/statistics/381088/global-market-share-of-power-generation-equipment-manufacturers/">http://www.statista.com/statistics/381088/global-market-share-of-power-generation-equipment-manufacturers/</a>

- Largest supplier of Transmission & Distribution (T&D) equipment in the United States, top three worldwide.

- http://microgridmedia.com/ge-becomes-globa-utility-td-powerhouse/

- https://medium.com/@GE\_Grid/a-vision-to-power-the-world-74349a3c98a6#.ehjw5t7v8

## Controls in The Era of Nation State Cyber Attacks

At RSA 2016, Admiral Michael Rogers, head of the NSA and the US Cyber Command, told delegates during his keynote address at RSA 2016 that the number one thing that keeps him awake at night is a cyber attack against US critical infrastructure, which is only a matter of when, not if, it will happen.

http://www.theregister.co.uk/2016/03/01/nsa\_boss\_three\_security\_nightmares/

**Stuxnet** compromised the control systems for Iran's nuclear centrifuges, rendering them useless. It attacked them successfully despite a state of the art air-gap defense.

http://threatjournal.com/archive/tj12072013.html

**Ukraine's** electric grid was shut down for 8 hours by a cyber attack, which wiped all control system computers, and bricked critical control interfaces. <a href="https://www.wired.com/2016/03/inside-cunning-unprecedented-hack-ukraines-power-grid/">https://www.wired.com/2016/03/inside-cunning-unprecedented-hack-ukraines-power-grid/</a>

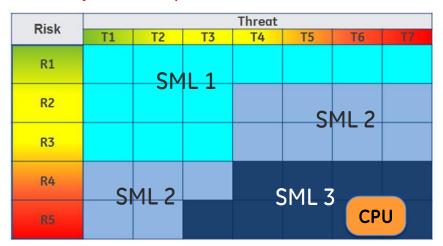

## How Much Security Do We Need? Strength of Mechanism Level (SML)

### Risk

- R1 Negligible consequences.

- **R2 Minimal damage** to security, safety, financial posture, or infrastructure.

- **R3** Some damage to the security, safety, financial posture, or infrastructure.

- **R4** Serious damage to the security, safety, financial posture, or infrastructure.

- **R5** Exceptionally **grave damage** to the security, safety, financial posture, or infrastructure.

### **Threat**

- T1 Inadvertent or accidental events.

- T2 Passive, casual adversary with minimal resources (e.g., listening, ...).

- **T3** Adversary with minimal resources; willing to take significant risk (hackers, ...).

- **T4** Sophisticated adversary with moderate resources; little risk (**organized crime**, ...).

- **T5** Sophisticated adversary with moderate resources; significant risk (**terrorists**, ...).

- T6 Extremely sophisticated adversary with abundant resources; little risk appetite (e.g., nation-state, ...).

- T7 Extremely sophisticated adversary with abundant resources; will to take extreme risk (e.g., nation-state in time of crisis).

<sup>\*</sup> Information Assurance Technical Framework, section 4.5, Release 3.1, National Security Agency, September 2002

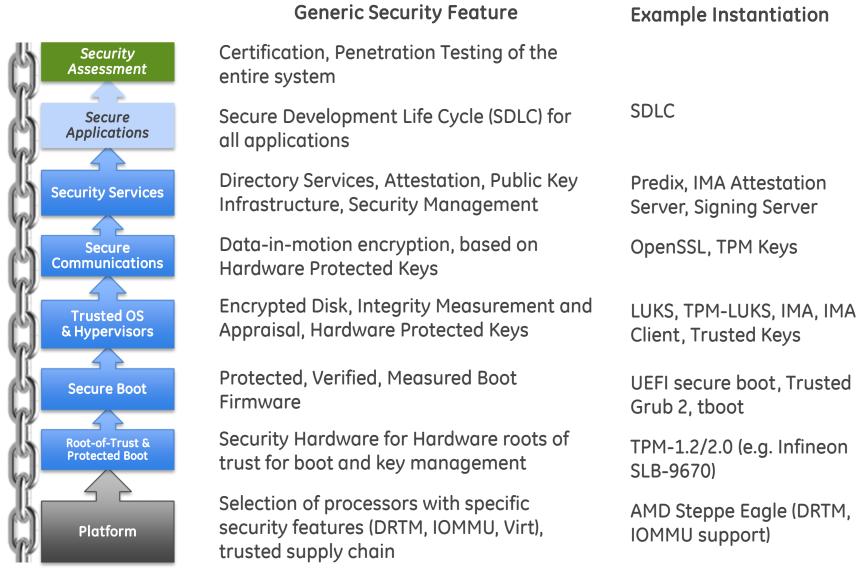

## A Hardware rooted Security Architecture for SML 3

### Specific Types of "Secure Boot"

- Protected Boot (e.g NIST SP-800-147, SPI-HPM, ROM'ed bootloader...)

- Boot firmware is write protected so it cannot be modified

- Essential base for all other boot versions

- Verified Boot (e.g. UEFI Secure Boot, "locked" bootloaders, appraisal...)

- Digital signature verification of boot sequence

- Active Defense: blocks system boot on verification failure

- Measured Boot (SRTM, DRTM)

- Collection of cryptographic hashes/signatures associated with boot environment

- Requires a measurement root-of-trust

- Provides audit trail and basis for attestation of platform integrity

- Passive Detection: does not block system from booting

- Seal & protect platform secrets based on platform integrity

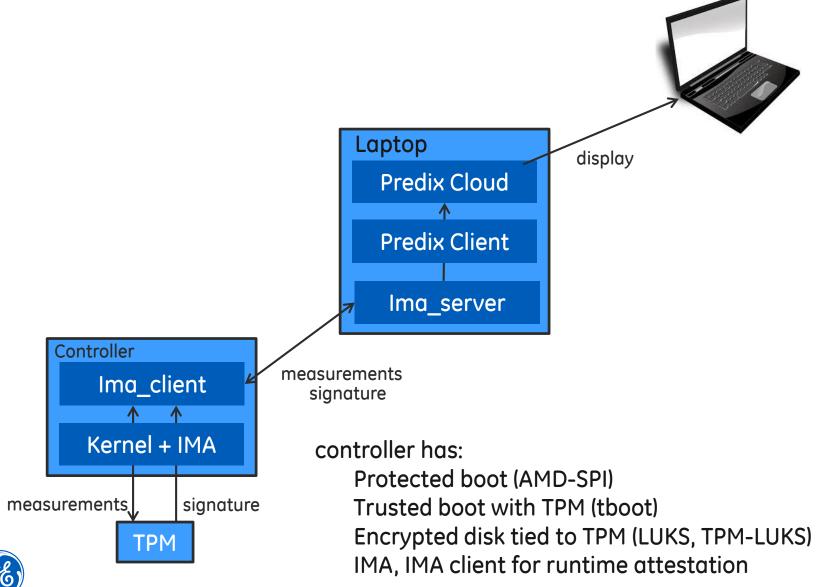

## Instantiating the Chain of Trust Across Platforms:

#### Intel/AMD

- UEFI

- Chipset based Protected Boot

- LPC TPM

- ARM, ARM + FPGA (TI, Freescale, Xilinx...)

- U-boot

- CPU/ROM based secure boot (sometimes requiring NDA)

- SPI TPM

- PPC (Freescale...)

- U-boot

- CPU/ROM based secure boot

- SPI TPM

- Virtualized

- KVM + swtpm + seabios

- Containers

# Linux/Platform Gaps/Issues

- TPM 2.0 Support (Thursday Evening BoF)

- Resource management (kernel and user space)

- Getting the boot log to the kernel (was acpi) -> UEFI table, Device Tree?

- Agreeing on APIs

- Measured and verified boot in UEFI Grub2 with TPM2 (Matthew Garrett)

- Container Filesystem User Namespace support (James Bottomley)

- Containers IMA Namespacing (Yuqiong Sun)

- Separate policies, measurement lists, vTPMs

- Hierarchical, easy to delete

- Hypervisor (KVM/QEMU) support for vTPM

- Support for measured and verified boot in UEFI/Legacy guest firmware.

# Linux/Platform Gaps/Issues

- SPI TPM driver in Linux (4.8RC) and u-boot (?)

- LUKS and Systemd support for Kernel Key Ring (e.g. from trusted keys)

- Or ext4 encryption?

- CPUs without public documentation on their processor based verified boot

- CPUs with binary blobs in: SMI, ME, trustzone

- Package signing tools

- Key management for third party signed files (less critical in embedded)

### Contributions

- tboot: (Safayet Ahmed)

- Security, Bug fixes

- AMD port with full DRTM

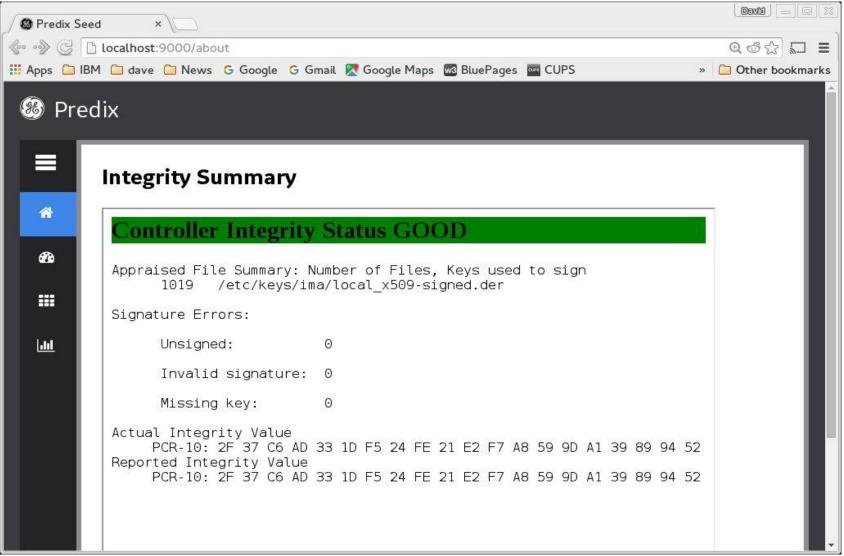

# Integrity PoC Demonstration

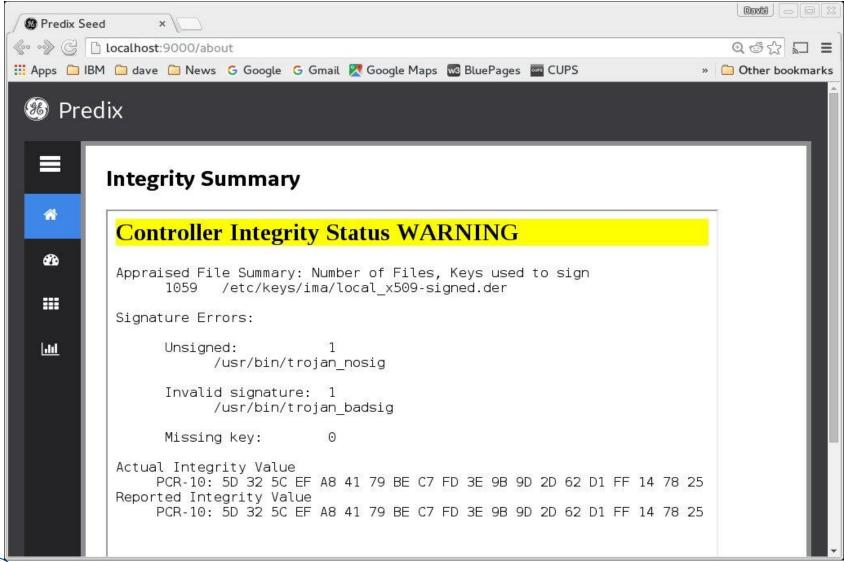

### Situation Normal

# Signed Measurements Show Attempt

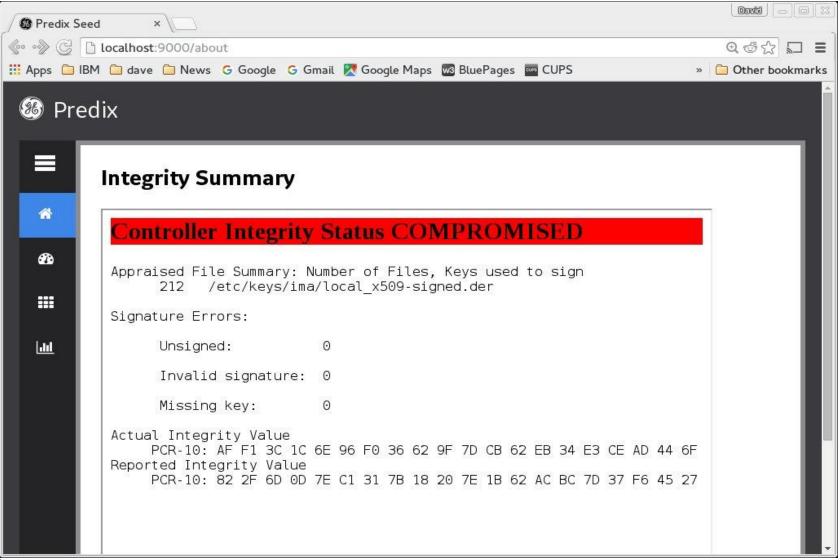

# TPM Signature Catches the Kernel Compromise

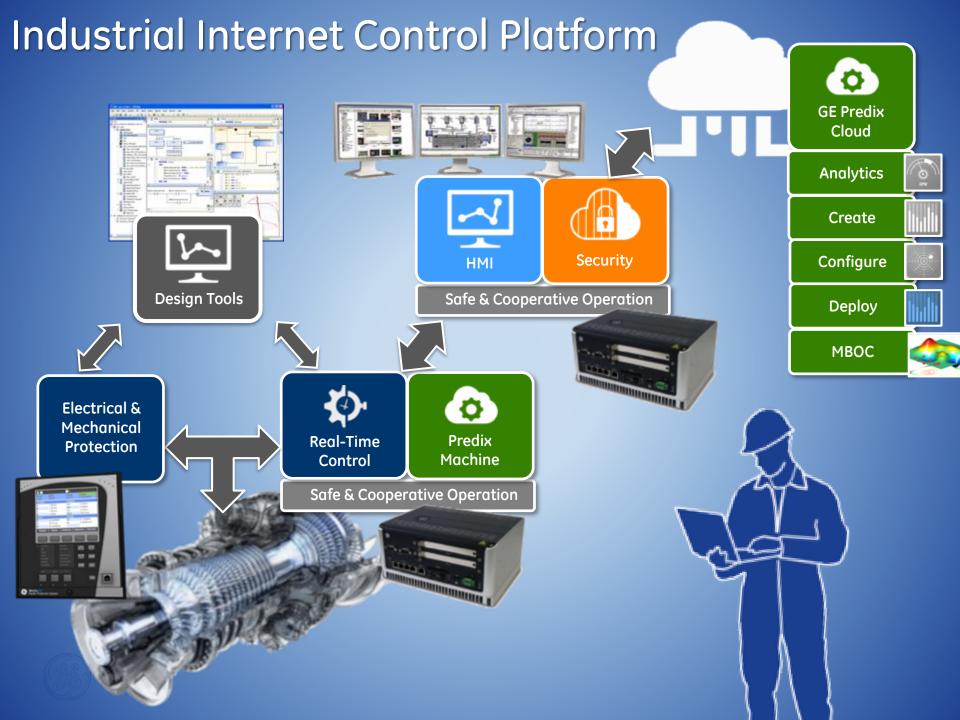

## Summary

- Nation State threat model

- Air Gaps keep you from knowing you've been hacked

- Industrial Control Systems Security Architecture

- Security from hardware through cloud

- Secure Hardware for multiple architectures (X86, ARM, PPC)

- Protected, Verified, Measured Boot

- Trusted OS

- Security Services

- Cloud based Attestation/Verification

- A Lot of Work Remaining